|

|

|

| |

发行人:黄建璋所长 编辑委员:曾雪峰教授 主编:林筱文 发行日期:2022.06.30 |

| |

|

|

|

本所吴育任教授指导硕士生张雨倢、沈雈莛同学荣获「The 5th International Workshop on Ultraviolet Materials and Devices (IWUMD 2022) Best Poster Paper Award」,特此恭贺!

|

|

|

|

|

|

| |

|

|

Study of Current Collapse Behaviors of Dual-gate AlGaN/GaN HEMTs on Si

Professor

Jian-Jang Huang’s Laboratory

Graduate Institute of Photonics and

Optoelectronics, National Taiwan University

台湾大学光电所 黄建璋教授

Surface traps on GaN-based HEMTs (high-electron-mobility transistors) usually

result in the increase of channel on-resistance. It becomes worsen when short

pulses are applied during high-frequency and high voltage switching. Here we

present a dual-gate transistor structure to suppress the dynamic on-resistance

increase. The auxiliary gate under a proper fixed voltage is able to induce

additional electrons to compensate the channel carrier loss during main gate

switching, leading to a lower dynamic on-resistance.

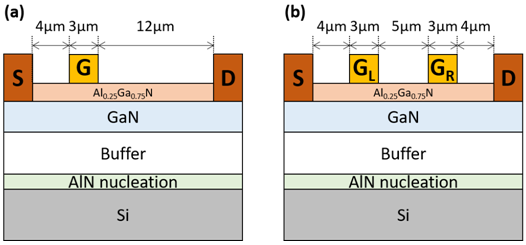

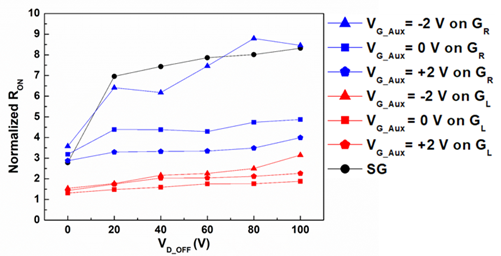

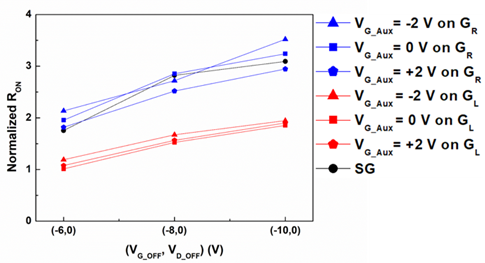

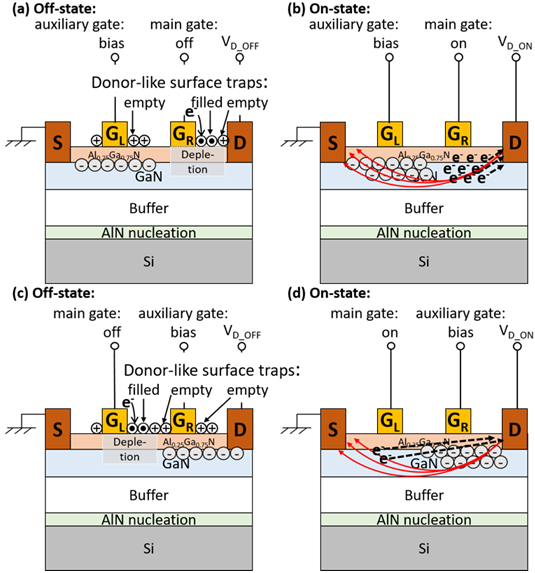

The dual-gate (DG) AlGaN/GaN HEMT is schematically shown in Fig. 1, along with a conventional device for comparisons. The DC electrical properties reveal that the drain current level of the DG-HEMT with GL-drive (main gate) and GR-float (auxiliary gate) is slightly higher than that of SG (single gate) -HEMT due to the additional carriers induced by the floating gate. The DG-HEMT with GR-drive and GL-float has the smallest current because of the largest gate-source resistance. When a bias voltage is applied on the auxiliary gate, the current level can be adjusted by the additional carriers. Since the auxiliary gate provides an extra source of supplying electrons to the channel that suffers from current collapse, we further studied current collapse phenomenon of the devices by a pulsed stress-measurement approach. The results suggest within the range of auxiliary gate bias, -2 ~ 2 V, a DG device with the main gate drive on GR and the auxiliary gate voltage of 0 V on GL has the lowest RON, while SG-HEMT is the worst in most of the stress conditions (see Fig. 2 for various drain and gate lag stresses). The improvement using the dual-gate structure is elucidated from the carrier distribution in the channel region as illustrated in Fig. 3. For the case main gate bias applied on GR and auxiliary bias on GL, the depleted carriers from the main gate can be quickly supplied by the carrier underneath the auxiliary electrode under a positive drain voltage with a slight negative impact of carriers recombined with traps on both sides of main gate. Finally, we conclude an auxiliary gate biased at 0 V near the source side results in the best suppress of current collapse.

|

|

|

Fig. 1. Cross-sectional epi-structure of (a) a SG-HEMT and (b) a DG-HEMT. |

|

|

|

Fig. 2. (a) Comparison of the normalized RON at various drain stress voltages, VD_OFF, and auxiliary gate biases. |

|

|

|

Fig. 2. (b) Comparison of the normalized RON at various gate lag stress conditions. |

|

|

|

Fig. 3. Distribution of electrons in the channel under various biases on the main gate and auxiliary gate electrodes. GR-drive/GL-bias at (a) off-state and (b) on-state. GL-drive/GR-bias at (c) off-state and (d) on-state. Note there may be small amount of donor-like surface traps (not shown) on both sides of GL and GR, depending on the bias voltage of the auxiliary gate. |

Mobility Enhancement in P-Type SnO Thin-Film Transistors via Ni Incorporation by Co-Sputtering

Professor I-Chun Cheng

Graduate Institute of Photonics and

Optoelectronics, National Taiwan University

台湾大学光电所 陈奕君教授

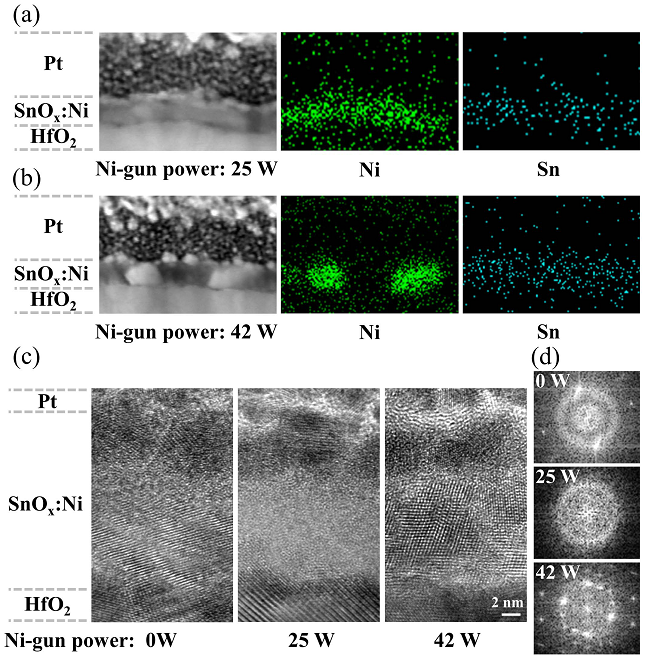

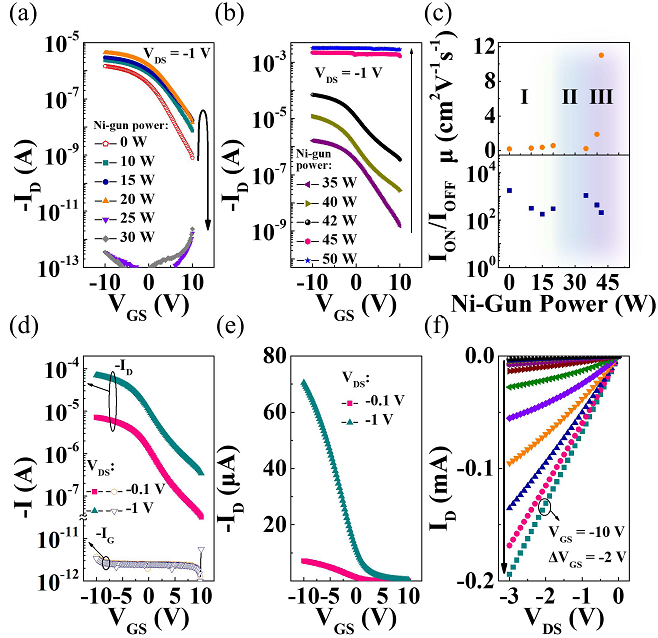

Oxide semiconductors have been considered one of the most promising candidates for flexible electronics applications owing to their low process temperatures and good reliability. However, the low mobility of p-type oxide semiconductors limits the performance of flexible oxide-TFT-based CMOS technology. In this study, p-type SnOx:Ni thin films were deposited by reactive rf magnetron co-sputtering, a technique compatible with the current industrial semiconductor manufacturing technology, from Sn and Ni targets. As the Ni-gun power increased, the distribution of Ni in the SnOx:Ni thin film changed from a more uniform dispersion to nanoclusters, resulting in the crystalline phase transition of SnOx:Ni from

α-SnO (110)-dominant polycrystalline to amorphous and then to α-SnO (101)-dominant polycrystalline. A high-mobility inverted-staggered p-type SnOx:Ni TFT was then fabricated on a glass substrate with a maximum process temperature of 225°C, which is compatible with flexible polymeric substrates. The TFT fabricated at an optimal Ni-gun power of 42 W exhibited an impressive field-effect mobility of 11 cm2V−1s−1 and on current of 35.2 μA per channel width-to-length ratio; these values are comparable to those of a typical n-type oxide TFT. These results should contribute toward flexible oxide-TFT-based CMOS technology. [IEEE Electron Device Letters, vol. 43, No. 2, pp. 228-231, Feb 2022]

|

|

|

Fig. 1. Elemental EDS maps of SnOx:Ni thin films deposited at Ni-gun powers of (a) 25 and (b) 42 W. (c) High-resolution TEM images and (d) corresponding fast Fourier transformed diffractograms of SnOx:Ni channels deposited at Ni-gun powers of 0, 25, and 42 W. |

|

|

|

Fig. 2. (a)(b) Transfer characteristics of SnOx:Ni TFTs fabricated with various Ni-gun powers. The channel width and length are 40 μm and 20 μm, respectively. (c) Electrical parameters of SnOx:Ni TFTs under different Ni-gun powers. Transfer characteristics in (d) log scale and (e) linear scale and (f) output characteristics of SnOx:Ni TFT fabricated with a Ni-gun power of 42 W. |

|

|

| |

|

|

|

|

|

| |

|

|

— 资料提供:影像显示科技知识平台 (DTKP, Display Technology

Knowledge Platform) —

—

整理:林晃岩教授、吴思洁 —

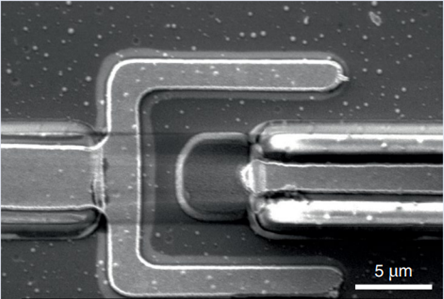

高效率的微型发光二极管

尺寸小于100×100 μm2的微米级发光二极管(μLED)有望成为扩增实境和虚拟实境等应用中之未来高分辨率显示器的关键技术。然而目前红光μLED的外部量子效率(external quantum efficiency, EQE)仅为0.1%左右。因为存在许多问题,包括Shockley-Read-Hall非辐射复合、强量子限制史塔克效应(Stark effect)及较差的晶体质量。现在,来自美国加州大学圣塔芭芭拉分校的Panpan Li及其同事展示了5×5 μm2尺寸的InGaN μLED(如图1),其发射波长为607 nm的琥珀色光,EQE最大值为2.6%(Appl. Phys. Lett. 120, 041102; 2022)。

透过大气压金属有机化学气相沉积(MOCVD),在极性c平面图案化蓝宝石基板上生长InGaN磊晶。蓝宝石上刻有小圆锥(高度为1.7μm,直径为2.6μm)。InGaN琥珀色μLED使用InGaN/GaN超晶格(superlattices)作为发光材料,并沉积Al/Ni/Au金属作为电极,用以施加驱动电流。

μLED侧壁区域发生的漏电流通常是由反应离子蚀刻(RIE)所造成的。为了抑制此问题,透过沉积30 nm厚的SiO2层来实现侧壁钝化。其钝化的效果透过在施加-5 V的电压下低至10-9 A的反向电流得到实验证实。

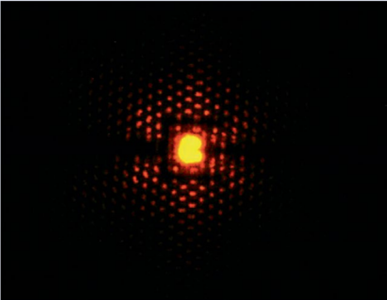

InGaN琥珀色μLED在注入3 A cm-2的电流密度下在607 nm处具有一个峰值,光谱半高全宽为44 nm。3 A cm–2处的发射光谱对应于国际照明委员会1931色度图中(x,y)点的(0.59, 0.36)处。随着注入电流密度从0.5增加到70 A cm-2,电致发光的峰值波长呈现从617到570 nm的大量蓝移。在20 A cm-2 下,输出功率和光通量分别为0.27 μW和1.27×10-4 lm。

与许多其它LED一样,μLED表现出效率下降的现象—当电流密度增加超过某个特定点时,EQE会下降。美国科学家通过制造5×5 μm2 和100×100 μm2 InGaN琥珀色μLED并比较它们的性能,研究了这种效率下降随组件尺寸如何变化。5×5 μm2与100×100 μm2组件相比,EQE下降趋势更大,这表明侧壁毁损所造成的非辐射复合的影响。科学家们认为,可以透过降低缺陷密度来进一步提高InGaN琥珀色μLED的EQE。

|

|

|

|

图1、InGaN琥珀色光μLED与其发光照片 |

|

参考资料: |

Horiuchi, N. “Efficient microscale emitters”

Nature Photonics volume

16, pages264 (2022)

https://doi.org/10.1038/s41566-022-00984-2

DOI:10.1038/s41566-022-00984-2

|

|

参考文献: |

Panpan Li, Hongjian Li, Yunxuan Yang, Haojun Zhang, Pavel Shapturenka, Matthew Wong, Cheyenne Lynsky, Mike Iza, Michael J. Gordon, James S. Speck, Shuji Nakamura, and Steven P. DenBaars, “Demonstration of ultra-small 5 × 5 μm2 607 nm InGaN amber micro-light-emitting diodes with an external quantum efficiency over 2%,” Appl. Phys. Lett. 120, 041102 (2022).

https://doi.org/10.1063/5.0078771

DOI:10.1063/5.0078771

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|